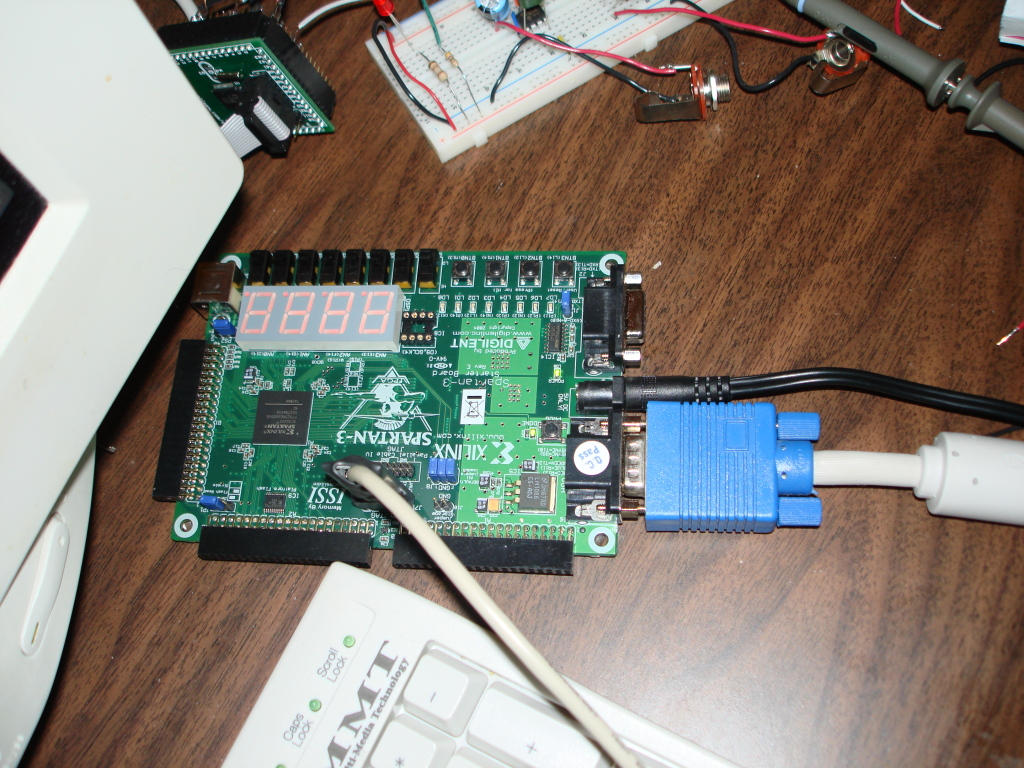

Spartan 3e Vga Example

The example code is in verilog, although converting the top level to VHDL if you prefer is a relatively trivial exercise. Here's a figure taken from the first application note showing the basic premise of the receiver: Since the Spartan 6 has got built-in SERDES hardware, these can be used as part of the deserialisation process. The Spartan-3E FPGA directly drives the five VGA signals via resistors. Each color line has a series resistor, with one bit each for VGARED, VGAGREEN and VGABLUE.

I'm trying to learn VHDL programming with some books and an Altera DE1 development kit from Terasic.

The issue here is that I am trying to program a VGA controller for work with a resolution of 640x480 (although my screen is an TFT LCD with 1280x1024).

I am having some problems with the code.

I am using a FSM to make the vertical and horizontal signals, another block to drive the RGB inputs and also a 27 MHz clock from the DE1.

I think there has to be something wrong with the code because the image I print on the screen is not the correct size (640x480) but bigger (approx. 1174x980).

By now I am trying to put one only color in the screen to simplify it until I can discover the mistake.

My project has 3 files, 1 for the block RGB, 1 for the FSM and another one to instantiate both of them.

I would appreciate some kind of help to solve this problem because I have tried hard to figure it out but I can't see where are the mistakes.

Thanks a lot!

Omar

VGA Controller file

FSM sync file

VGD display file

cbmeeks

2 Answers

See full details on VGA theory and VHDL code for VGA controllers in chapter 15 of 'Circuit Design and Simulation with VHDL', 2nd edition (only in the 2nd edition), 2010, by V. A. Pedroni.

I think your monitor is syncing to your output and simply displaying the video full screen, much as your TV might with an auxiliary input.

I worked out your H and V rates in terms of your reported 27 MHz (~ 37 ns) and see if I could find a 1280 x 1024 LCD monitor that would accept them.

Your horizontal counter is counter2 which counts from 0 to number_pixelsMAX_H - 1(799), and your vertical counter is counter3 which counts from 0 to number_pixelsMAX_V - 1 (524).

That gives you a horizontal rate of 800 x 37 ns = 29.600 us and a vertical rate of 15.54 ms. 33.8 KHz H, V 64 Hz.

Without knowing the specific monitor you're using I looked around for any spec for one and found an SXGA AMOLED display spec that defines the sync rate range.

On page 14 there's a table showing the H and V ranges:

It shows that this particular LCD panel could display your frame rate. How the pixel clock for it would be recovered from sync signals is dependent on a monitor build using this particular display.

All versions of the DE1 board appear to use the same ADV7123 to convert your SVGA signal to analog transmitted across a 15 pin VGA connector.

I think it highly likely your SXGA rate monitor capable of displaying SVGA.

Spartan 3e Fpga

It looks like an Acer 17 inch V173L will sync to it for instance having 3 VGA modes (60 Hz, 72 Hz, and 75 Hz) and a Mac mode for 640 x 480 (66 Hz).

The ability to synchronize to multiple scan rates is very common in monitors these days.

My six year old Dell 2208WP is telling me I'm inputting a DVI-D signal of 1680x1050 at 60 Hz. I can tell my Mac to switch resolution and will faithfully follow, adhering to presets conveyed by the DVI interface, in this case limited to 1024x640 (which resized all my open windows, flattening them).

Depending on your monitor you should get multi-syncing across a wider range with an analog input (which the DE1 provides).

The mechanism that makes it work for an analog video input is the pixel clock to the LCD panel is related to the un-blanked portion of a horizontal line, delivering a number of pixel clocks during that interval that matches the panel resolution, re-converting analog video to digital at a rate that fills all (or nearly all) the screen pixels.

user1155120user1155120Not the answer you're looking for? Browse other questions tagged vhdlfpgavga or ask your own question.

| Title | color_maker-s3esk (simple VGA tester) |

| Author | Nikolaos Kavvadias (C) 2014, 2015, 2016 |

| Contact | nikos@nkavvadias.com |

| Source | Mike Field (for the VGA controller; see AUTHORS) |

| Website | http://www.nkavvadias.com |

| Release Date | 08 August 2016 |

| Version | 1.1.1 |

| Rev. history | |

| v1.1.1 | 2016-08-08 Added clean-up script. |

| v1.1.0 | 2016-07-10 GHDL simulation scripts and generation of log file forVGA simulation. |

| v1.0.2 | 2016-07-10 Update for 2016. |

| v1.0.1 | 2014-06-18 Changed README to README.rst; COPYING to LICENSE. |

| v1.0.0 | 2014-06-09 Initial release for the Spartan-3E Starter kit board. |

1. Introduction

color_maker is a simple design for testing VGA output. This version of thecolor_maker produces 3-bit RGB color (R1G1B1) as supported by the XilinxSpartan-3E starter kit board. 3 out of the 4 available slide switches(specifically switches SW2, SW1, SW0) are used for setting a specific colorout of the eight unique colors that are available.

The following table summarizes the available colors.

| R | G | B | Description |

|---|---|---|---|

| 0 | 0 | 0 | Black (Noir) |

| 0 | 0 | 1 | Blue |

| 0 | 1 | 0 | Green |

| 0 | 1 | 1 | Cyan |

| 1 | 0 | 0 | Red |

| 1 | 0 | 1 | Magenta |

| 1 | 1 | 0 | Yellow |

| 1 | 1 | 1 | White |

For the standard VGA resolution (640x480@60Hz), a 25MHz clock is used, asproduced by the clockdiv clock divider (divide by 2). The VGA controlleris implemented by vgactrl.vhd. The color selection logic is verysimple and directly assigns SW2 to the R, SW1 to G and SW0 to the B component.For 800x600@72Hz, a 50 MHz clock should be used.

The vga_controller design has been adapted from the work by Mike Field:http://hamsterworks.co.nz/mediawiki/index.php/Hidef_snow

2. File listing

The color_maker distribution includes the following files:

| /color_maker-s3esk | Top-level directory |

| AUTHORS | List of authors. |

| LICENSE | 3-clause modified BSD license. |

| README.rst | This file. |

| README.html | HTML version of README.rst. |

| README.pdf | PDF version of README.rst. |

| clean.sh | A bash script for cleaning simulation artifacts. |

| clockdiv.vhd | Configurable, portable, clock divider. |

| color_maker.vhd | Color assignment logic. |

| color_maker_top.ucf | User Constraints File for the XC3S500E-FG320-4device. |

| color_maker_top.vhd | The top-level RTL VHDL design file. |

| color_maker_top_tb.vhd | Testbench for the top-level RTL VHDL design file. |

| color_maker_top-syn.sh | Bash shell script for synthesizing thecolor_maker design with Xilinx ISE. |

| ghdl.mk | Makefile for VHDL simulation with GHDL. |

| ghdl.sh | Bash shell script for running the simulation withGHDL. |

| impact_s3esk.bat | Windows Batch file for automatically invoking XilinxIMPACT in order to download the generated bitstreamto the target hardware. |

| rst2docs.sh | Bash script for generating the HTML and PDF versions. |

| vgactrl.vhd | RTL VHDL code for the VGA controller. |

| xst.mk | Standard Makefile for command-line usage of ISE. |

Spartan 3e Vga Example 3

3. Usage

The color_maker distribution includes scripts for logic synthesis automationsupporting Xilinx ISE. The corresponding synthesis script can be edited in orderto specify the following for adapting to the user's setup:

XDIR: the path to the/binsubdirectory of the Xilinx ISE/XSTinstallation where thexst.exeexecutable is placedarch: specific FPGA architecture (device family) to be used for synthesispart: specific FPGA part (device) to be used for synthesis

3.1. Running the simulation script

This step assumes that the GHDL executable is in the user's $PATH, e.g., byusing:

Then the simulation shell script can be run from a UNIX/Linux/Cygwin command line:

This will produce a text file named color_maker_top_results.txt with the valuesof current time whenever a clock event occurs (as integer) and the signals hs,vs, red, green and blue (as binary). This can be used by an externaltool, the VGA simulator (http://ericeastwood.com/lab/vga-simulator/) for visualizingthe outcome if a VGA/CRT monitor would be driven. A downloadable version of theVGA simulator also exists: https://github.com/MadLittleMods/vga-simulator

In order to work with the VGA simulator without further changes, the red, green andblue signals are extended to 3, 3, and 2 bits, respectively in the testbench.

To clean up simulation artifacts, including the generated diagnostics file, usethe clean.sh script:

3.2. Running the synthesis script

For running the Xilinx ISE synthesis tool, generating FPGA configurationbistream and downloading to the target device, execute the corresponding scriptfrom within the color_maker-s3esk directory:

In order to successfully run the entire process, you should have the targetboard connected to the host and it should be powered on.

The synthesis procedure invokes several Xilinx ISE command-line tools for logicsynthesis as described in the corresponding Makefile, found in thethe color_maker-s3esk directory.

Typically, this process includes the following:

- Generation of the

*.xstsynthesis script file. - Generation of the

*.ngcgate-level netlist file in NGC format. - Building the corresponding

*.ngdfile. - Performing mapping using

mapwhich generates the corresponding*.ncdfile. - Place-and-routing using

parwhich updates the corresponding*.ncdfile. - Tracing critical paths using

trcefor reoptimizing the*.ncdfile. - Bitstream generation (

*.bit) usingbitgen, however with unused pins.

Spartan 3e Vga Example 1

As a result of this process, the color_maker_top.bit bitstream file isproduced.

Then, the shell script invokes the Xilinx IMPACT tool by a Windows batch file,automatically passing a series of commands that are necessary for configuringthe target FPGA device:

- Set mode to binary scan.

- Set cable port detection to auto (tests various ports).

- Identify parts and their order in the scan chain.

- Assign the bitstream to the first part in the scan chain.

- Program the selected device.

- Exit IMPACT.

4. Prerequisites

- [suggested] Linux (e.g., Ubuntu 16.04 LTS) or MinGW environment on Windows 7 (64-bit).

- [suggested] GHDL simulator: http://ghdl.free.frThe 0.33 version on Linux Ubuntu 16.04 LTS was used.

- [optional] The VGA simulator: http://ericeastwood.com/lab/vga-simulator/

- Xilinx ISE (free ISE webpack is available from the Xilinx website):http://www.xilinx.com.The 14.6 version on Windows 7/64-bit is known to work.